# L99SM81V

# Programmable stepper motor driver for automotive applications with micro-stepping and stall detection

Datasheet - Production data

#### **Features**

- AEC-Q100 qualified

- Stepper motor driver with up to 1.35 A current capability

- Programmable Step mode:

- Full step, Half step, Mini step, 1/8 Micro step, 1/16 Micro step

- Current regulation by integrated PWM control with fully integrated current sensing

- Equivalent 10 bit resolution on current regulation loop:

- Two 4-bit programmable full scale current amplitudes: one for RUN and one for HOLD mode

- 6-bit DAC for reference current generation (whatever programmed full scale amplitude)

- 4 programmable decay modes:

- Slow-mode, mixed-mode and 2x automatically selected decay-modes

- 3x programmable inputs for direct control of step clock, direction, hold and step modes

- 1x programmable analog output for T<sub>j</sub> measurement or band-gap reference

- 2x programmable digital outputs for internally generated PWM ON duty cycles,

- error signals, coils voltage measurement synchronization signals

- Programmable MOSFETs switching speed: four options for EMC and power dissipation trade-off optimization

- PWM frequency wobbling for reduction of conducted EM energy

- Outputs protection and diagnosis (open load, short to battery, short to GND)

- Integrated ADC for coil voltage measurement and stall detection

- 5 V low drop voltage regulator short-circuit protected

- Very low current consumption in standby mode (typ. 10 μA)

- Thermal warning and shutdown

- ST SPI 4.1 interface for control and diagnostics

## **Applications**

Bipolar 2 phase stepper motor driver for automotive applications like adaptive front light systems or projectors for head-up displaying

## **Description**

The L99SM81V is an automotive grade integrated driver for bipolar two-phase stepper motors capable of current controlled microstepping with programmable amplitude. The device features a 5 V voltage regulator to supply external sensors.

The integrated Serial Peripheral Interface (SPI) makes it possible to adjust device parameters, control all operating modes and read out diagnostic information. Digital I/Os are also optionally usable for more flexible and reliable application control.

Contents L99SM81V

# **Contents**

| lock di | agram an         | d pin description                                              | 8    |

|---------|------------------|----------------------------------------------------------------|------|

| evice c | lescriptio       | n                                                              | 11   |

| 2.1     | Supply pi        | ns (VS, VREG, VDD)                                             | 11   |

| 2.2     | Voltage re       | egulator (V5V)                                                 | 11   |

| 2.3     | Charge P         | ump (CP)                                                       | 11   |

| 2.4     | Standby r        | mode (EN)                                                      | 11   |

| 2.5     | Application      | n block diagram                                                | 12   |

| 2.6     | Stepping         | modes and step update                                          | 12   |

| 2.7     | Current re       | eferences generation and PWM regulation                        | 16   |

| 2.8     | HOLD mo          | ode                                                            | 17   |

| 2.9     | Decay mo         | odes                                                           | 17   |

|         | 2.9.1            | DMR[1:0] bits = 01b, DMH = 0 - Slow decay mode always applie   |      |

|         | 2.9.2            | DMR[1:0] bits = 10b, DMH = 1 - Mixed decay mode always applied | ed19 |

|         | 2.9.3            | DMR[1:0] bits = 00b - Auto decay mode 1                        | 21   |

|         | 2.9.4            | DMR[1:0] bits = 11b - Auto decay mode 2                        | 24   |

| 2.10    | Control pi       | ns (CTRLx)                                                     | 26   |

|         | 2.10.1           | Step Control (STEP)                                            |      |

|         | 2.10.2           | Direction Control (DIR)                                        |      |

| 0.44    | 2.10.3           | Step mode Control (SMODE) and HOLD mode                        |      |

| 2.11    | J                | tputs                                                          |      |

|         | 2.11.1           | Error/ warning indicator (ERR)                                 |      |

|         | 2.11.2<br>2.11.3 | Error/ warning change indicator (EC)                           |      |

|         | 2.11.3           | Coil Voltage Conversion Ready (CVRDY)                          |      |

|         | 2.11.5           | Coil Voltage Runaway (CVRUN)                                   |      |

|         | 2.11.6           | Coil Voltage Lower Limit Underrun (CVLL)                       |      |

| 2.12    | Analog ou        | ıtput                                                          |      |

| 2.13    | Motor coi        | ·<br>I voltage measurement for stall detection                 | 29   |

|         | 2.13.1           | Coil voltage measurement triggering                            |      |

|         | 2.13.2           | Coil voltage measurement processing                            | 30   |

| 2.14    | Serial per       | ipheral interface (ST SPI standard)                            | 31   |

| rotecti | ons and d        | liagnostics                                                    | 33   |

| 3.1     |                  | agnostics                                                      |      |

|         | 3.1.1            | VS overvoltage and undervoltage                                |      |

| L99SM81V | Contents |

|----------|----------|

|          |          |

|   | . Oi i i egi | J.C. J         |                                      |    |

|---|--------------|----------------|--------------------------------------|----|

| 6 |              | · ·            |                                      |    |

|   | 5.6          |                | GOD and Fayload inconsistency        |    |

|   |              | 5.5.1<br>5.5.2 | Register change during communication |    |

|   | 5.5          | •              | ntation remarks                      |    |

|   | EE           | 5.4.5          | Data Stuck                           |    |

|   |              | 5.4.4          | CSN timeout                          |    |

|   |              | 5.4.3          | SCK Phase (CPHA) check               |    |

|   |              | 5.4.2          | SCK Polarity (CPOL) check            |    |

|   |              | 5.4.1          | Clock monitor                        |    |

|   | 5.4          | Protocol       | failure detection                    | 53 |

|   |              | 5.3.2          | Device Application Registers         | 53 |

|   |              | 5.3.1          | Device Information Register          | 51 |

|   | 5.3          | Address        | and data definition                  | 51 |

|   |              | 5.2.2          | SDO Frame                            | 49 |

|   |              | 5.2.1          | SDI frame                            | 47 |

|   | 5.2          | Protocol.      |                                      | 47 |

|   | 5.1          | Physical       | layer                                | 46 |

| 5 | ST SPI p     | orotocol       |                                      | 46 |

|   | 4.6          | SPI bus (      | (CSN, SCK, SDI, SDO)                 | 43 |

|   | 4.5          |                | ctrical characteristics              |    |

|   | 4.4          |                | data                                 |    |

|   | 4.3          | •              | ection                               |    |

|   | 4.2          | •              | g range                              |    |

|   | 4.1          |                | maximum ratings                      |    |

| 4 |              |                | teristics                            |    |

|   | <b>-</b> 1   | 3.4.2          | Open load detection                  |    |

|   |              | 3.4.1          | Overcurrent detection                |    |

|   | 3.4          |                | agnostic                             |    |

|   | 3.3          |                | rrent protection (dead-time)         |    |

|   | 3.2          |                | warning and thermal shutdown         |    |

|   | • -          | 3.1.6          | VDD failure                          |    |

|   |              | 3.1.5          | V5V failure                          |    |

|   |              | 3.1.4          | V5V undervoltage warning             |    |

|   |              | 3.1.3          | CP failure                           |    |

|   |              | 3.1.2          | VREG overvoltage and undervoltage    | 33 |

| Content | ts       |                                               | L99SM81V |

|---------|----------|-----------------------------------------------|----------|

|         | 6.1      | Register map overview                         | 55       |

|         | 6.2      | Global Status Register GSR (0x01)             | 56       |

|         | 6.3      | Motor and driver Status Register MSR (0x02)   | 58       |

|         | 6.4      | Global Configuration Register 1 GCR1 (0x03)   | 60       |

|         | 6.5      | Global Configuration Register 2 GCR2 (0x04)   | 62       |

|         | 6.6      | Motor Control Register 1 MCR1 (0x05)          | 63       |

|         | 6.7      | Motor Control Register 2 MCR2 (0x06)          | 65       |

|         | 6.8      | Motor Control Register 3 MCR3 (0x07)          | 67       |

|         | 6.9      | Motor current reference register MCREF (0x08) | 68       |

|         | 6.10     | Motor Coil Voltage 0° MCVA (0x09)             | 69       |

|         | 6.11     | Motor Coil Voltage 90° MCVB (0x0A)            | 70       |

|         | 6.12     | Motor Coil Voltage 180° MCVC (0x0B)           | 71       |

|         | 6.13     | Motor Coil Voltage 270° MCVD (0x0C)           | 72       |

|         | 6.14     | Motor Coil Voltage Low Limit B MCVLLB (0x0D)  | 73       |

|         | 6.15     | Motor Coil Voltage Low Limit A MCVLLA (0x0E)  | 74       |

|         | 6.16     | Motor Coil Voltage Upper Limit MCVUL (0x0F)   | 75       |

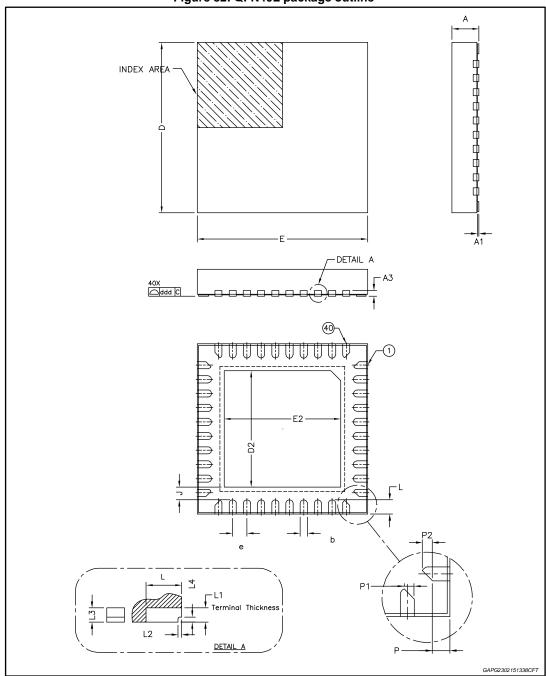

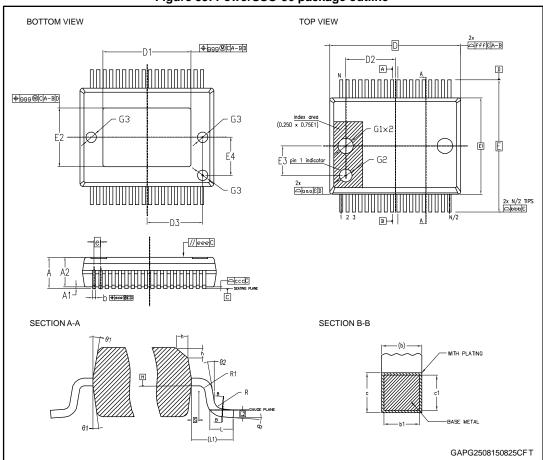

| 7       | Package  | e information                                 | 76       |

|         | 7.1      | QFN40L package information                    | 76       |

|         | 7.2      | PowerSSO-36 package information               |          |

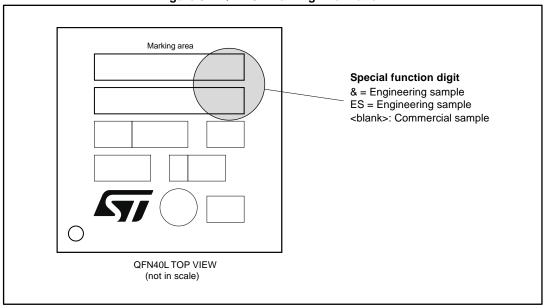

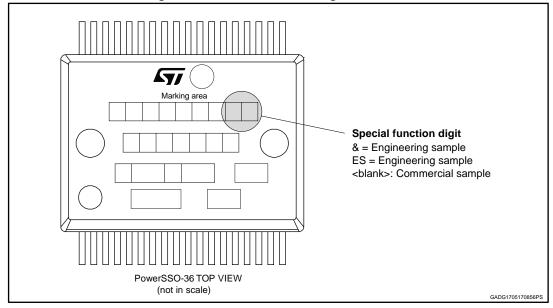

|         | 7.3      | Marking information                           |          |

| 8       | Order co | odes                                          |          |

|         |          | ı history                                     |          |

| •       | こしているこしし | I IIIJLVI V                                   | 02       |

L99SM81V List of tables

# List of tables

| Table 1: Pin definition and function                               |    |

|--------------------------------------------------------------------|----|

| Table 2: Coil voltage synopsis table                               | 30 |

| Table 3: Absolute maximum ratings                                  |    |

| Table 4: Operating range                                           | 35 |

| Table 5: ESD protection                                            | 35 |

| Table 6: Thermal data                                              | 36 |

| Table 7: Thermal warning and thermal shutdown                      |    |

| Table 8: Supply and supply monitoring                              | 36 |

| Table 9: Power on reset                                            | 38 |

| Table 10: Voltage regulator V5V                                    |    |

| Table 11: AOUT electrical characteristics                          |    |

| Table 12: OUTxn outputs (x = A,B; n = 1,2)                         |    |

| Table 13: Charge pump                                              |    |

| Table 14: PWM control                                              |    |

| Table 15: Clock characteristics                                    | 42 |

| Table 16: Digital inputs CTRL1, CTRL2, CTRL3, EN                   |    |

| Table 17: Coil voltage acquisition                                 | 42 |

| Table 18: Digital outputs DOUT1, DOUT2                             |    |

| Table 19: CSN, SCK, SDI input                                      |    |

| Table 20: SDO output                                               |    |

| Table 21: SPI timing                                               |    |

| Table 22: Operation codes                                          |    |

| Table 23: Device application access                                |    |

| Table 24: Device information read access                           |    |

| Table 25: Address range                                            |    |

| Table 26: Global Status Byte GSB                                   |    |

| Table 27: Global Status Byte GSB (bit description)                 |    |

| Table 28: Device information read access operation code            |    |

| Table 29: Device information registers                             |    |

| Table 30: SPI mode                                                 |    |

| Table 31: SPI Burst Read                                           |    |

| Table 32: SPI data length                                          |    |

| Table 33: SPI data consistency check                               |    |

| Table 34: Complete device SPI register table                       |    |

| Table 35: Global Status Register GSR                               |    |

| Table 36: Global Status Register GSR (bit description)             |    |

| Table 37: Motor and driver Status Register MSR                     |    |

| Table 38: Motor and driver Status Register MSR (bit description)   |    |

| Table 39: Global Configuration Register 1 GCR1                     | 60 |

| Table 40: Global Configuration Register 2 GCR2                     |    |

| Table 41: Global Configuration Register 2 GCR2 (bit description)   |    |

| Table 43: Motor Control Register 1 MCR1                            |    |

| Table 44: Motor Control Register 1 MCR1 (bit description)          |    |

| Table 45: Motor Control Register 2 MCR2                            |    |

| Table 46: Motor Control Register 2 MCR2 (bit description)          |    |

| Table 47: Motor Control Register 3 MCR3                            |    |

| Table 48: Motor Control Register 3 MCR3 (bit description)          |    |

| Table 49: Motor current reference register MCREF                   |    |

| Table 50: Motor Current reference register MCREF (bit description) |    |

| Table 50: Motor Coil Voltage 0° MCVA                               |    |

| Table 52: Motor Coil Voltage 0° MCVA (bit description)             | 60 |

| Table 53: Motor Coil Voltage 90° MCVB                              | 7∩ |

| Table del Motor dell' voltage del Move                             |    |

List of tables L99SM81V

| Table 54: Motor Coil Voltage 90° MCVB (bit description)           | 70 |

|-------------------------------------------------------------------|----|

| Table 55: Motor Coil Voltage 180° MCVC                            |    |

| Table 56: Motor Coil Voltage 180° MCVC (bit description)          |    |

| Table 57: Motor Coil Voltage 270° MCVD                            |    |

| Table 58: Motor Coil Voltage 270° MCVD (bit description)          |    |

| Table 59: Motor Coil Voltage Low Limit B MCVLLB                   |    |

| Table 60: Motor Coil Voltage Low Limit B MCVLLB (bit description) | 73 |

| Table 61: Motor Coil Voltage Low Limit A MCVLLA                   |    |

| Table 62: Motor Coil Voltage Low Limit A MCVLLA (bit description) |    |

| Table 63: Motor Coil Voltage Upper Limit MCVUL                    | 75 |

| Table 64: Motor Coil Voltage Upper Limit MCVUL (bit description)  |    |

| Table 65: QFN40L package mechanical data                          |    |

| Table 66: PowerSSO-36 package mechanical data                     |    |

| Table 67: Device summary                                          |    |

| Table 68: Document revision history                               |    |

L99SM81V List of figures

# List of figures Figure 1: Block diagram (OFN40L)

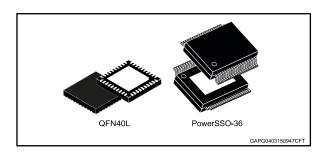

| Figure 1: Block diagram (QFN40L)                                                                  | 8  |

|---------------------------------------------------------------------------------------------------|----|

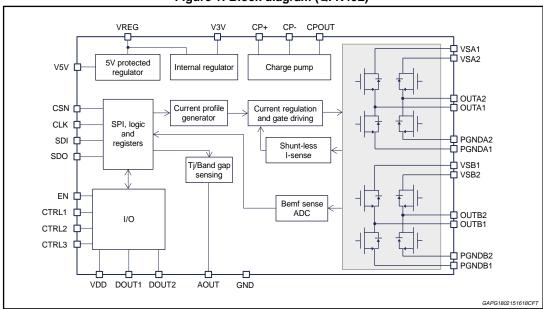

| Figure 2: Block diagram (PowerSSO-36)                                                             |    |

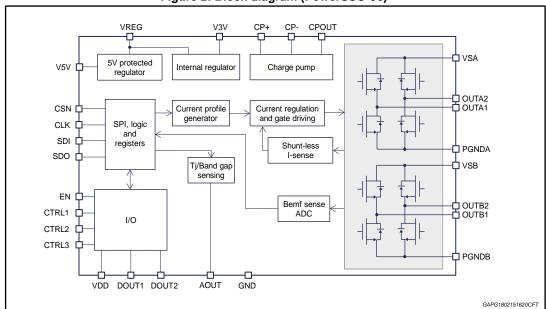

| Figure 3: QFN40 pin connections (top view)                                                        | 9  |

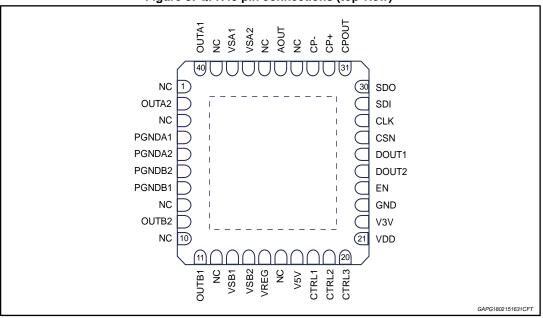

| Figure 4: PSSO36 pin connections (top view)                                                       | 9  |

| Figure 5: Stepper motor driver application block diagram                                          |    |

| Figure 6: Electrical revolution in 1/16th micro step (current profile and phase counter values)   |    |

| Figure 7: Electrical revolution in 1/8th micro step (current profile and phase counter values)    |    |

| Figure 8: Electrical revolution in mini step (current profiles and phase counter values)          |    |

| Figure 9: Electrical revolution in half step (current profiles and phase counter values)          |    |

| Figure 10: Electrical revolution in full step mode (current profiles and phase counter values)    |    |

| Figure 11: Current reference generation block diagram                                             |    |

| Figure 12: PWM ON and PWM OFF switching states                                                    |    |

| Figure 13: PWM switching sequence (slow decay)                                                    |    |

| Figure 14: Mixed decay                                                                            | 19 |

| Figure 15: Mixed decay (current undershoot / limit not reached)                                   | 20 |

| Figure 16: Electrical revolution in auto decay mode 1 (DIR = 1)                                   |    |

| Figure 17: Electrical revolution in auto decay mode 1 (DIR = 0)                                   |    |

| Figure 18: Auto decay mode 1 with direction change                                                | 23 |

| Figure 19: Auto decay mode 2, DIR = 0                                                             |    |

| Figure 20: Auto decay mode 2, behavior at micro-step change (dead-time omitted)                   | 25 |

| Figure 21: Comparative Auto decay mode 1 vs. Auto decay mode 2                                    |    |

| Figure 22: CTRL pin multiplex options                                                             |    |

| Figure 23: Configurable I/O multiplex options                                                     |    |

| Figure 24: PWM signal generation                                                                  |    |

| Figure 25: Coil voltage registers content (DIR = 0, positive current flowing from OUTx1 to OUTx2; |    |

| Figure 26: Coil voltage measurement sequence example                                              |    |

| Figure 27: SPI transfer timing diagram                                                            |    |

| Figure 28: SPI timing diagram                                                                     |    |

| Figure 29: SPI pin description                                                                    |    |

| Figure 30: SDI frame                                                                              |    |

| Figure 31: SDO frame                                                                              |    |

| Figure 32: QFN40L package outline                                                                 |    |

| Figure 33: PowerSSO-36 package outline                                                            |    |

| Figure 34: QFN40L marking information                                                             |    |

| Figure 35: PowerSSO-36 marking information                                                        | 80 |

# 1 Block diagram and pin description

Figure 1: Block diagram (QFN40L)

Figure 2: Block diagram (PowerSSO-36)

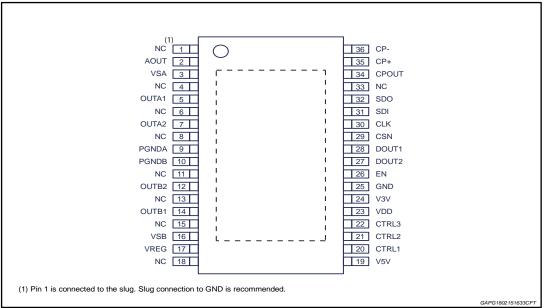

Figure 3: QFN40 pin connections (top view)

Figure 4: PSSO36 pin connections (top view)

Table 1: Pin definition and function

| Symbol | Function                                                          | I/O Type |

|--------|-------------------------------------------------------------------|----------|

| NC     | Not connected                                                     |          |

| OUTA1  | Output of leg 1 of H-Bridge A                                     | 0        |

| OUTA2  | Output of leg 2 of H-Bridge A                                     | 0        |

| PGNDAn | Power ground for leg n of H-Bridge A (QFN40 option only; n = 1,2) | PGND     |

| PGNDA  | Power ground for H-Bridge A (PSSO36 only)                         | PGND     |

577

| Symbol | Function                                                            | I/O Type |

|--------|---------------------------------------------------------------------|----------|

| PGNDBn | Power ground for leg n of H-Bridge B (QFN40 option only; n = 1,2)   | PGND     |

| PGNDB  | Power ground for H-Bridge B (PSSO36 option only)                    | PGND     |

| OUTB2  | Output of leg 2 of H-Bridge B                                       | 0        |

| OUTB1  | Output of leg 1 of H-Bridge B                                       | 0        |

| VSBn   | Supply voltage for leg n of H-Bridge B (QFN40 option only; n = 1,2) | Supply   |

| VSB    | Supply voltage for H-Bridge B (PSSO36 option only)                  | Supply   |

| VSAn   | Supply voltage for leg n of H-Bridge A (QFN40 option only; n = 1,2) | Supply   |

| VSA    | Supply voltage for H-Bridge A (PSSO36 option only)                  | Supply   |

| CTRL3  | Configurable control pin 3                                          | I        |

| CTRL2  | Configurable control pin 2                                          | I        |

| CTRL1  | Configurable control pin 1                                          | I        |

| VREG   | Supply voltage for 5 V regulator                                    | Supply   |

| V5V    | 5 V regulator output                                                | 0        |

| VDD    | Digital I/Os supply                                                 | Supply   |

| V3V    | Internal 3V regulator decoupling output                             | 0        |

| GND    | GND connection                                                      | GND      |

| EN     | Enable input                                                        | I        |

| DOUT2  | Configurable digital output 2                                       | 0        |

| DOUT1  | Configurable digital output 1                                       | 0        |

| CSN    | SPI chip select NOT input                                           |          |

| CLK    | SPI serial clock input                                              | I        |

| SDI    | SPI serial data input                                               | I        |

| SDO    | SPI serial data output                                              | 0        |

| CPOUT  | Charge pump output                                                  | 0        |

| CP+    | Charge pump pin for capacitor, positive side                        | 0        |

| CP-    | Charge pump pin for capacitor, negative side                        | 0        |

| AOUT   | Analog Output                                                       | 0        |

## 2 Device description

## 2.1 Supply pins (VS, VREG, VDD)

The device has three different supply input pins:

VSx pins are used to supply the four H-bridges, VSA pin(s) is (are) also used to supply the charge pump. All of VS pins must be protected against negative voltages.

- VREG pin supplies the embedded 5 V LDO regulator and the 3.3 V regulator supplying internal logic. It must be protected against negative voltages

- VDD supplies all of the digital I/Os, it is intended to be equal to the voltage used to supply the application micro-controller; both 3.3 V and 5 V are supported.

#### 2.2 Voltage regulator (V5V)

The device integrates a low-drop voltage regulator capable of supplying external devices (e.g. external sensors) with a continuous load current up to 50 mA. The output voltage is stable with ceramic output capacitors equal to 220 nF or bigger, placed close to the device. The voltage regulator is protected against short circuit to both GND and battery (for the latter, VREG must be present).

## 2.3 Charge Pump (CP)

L99SM81V embeds a single stage charge pump which requires a 'flying' external ceramic capacitor placed in between pins CP+ and CP- and an additional ceramic capacitor on pin CP. The charge pump operation is internally monitored and a condition that avoids proper operation of the charge pump will be indicated by the respective SPI diagnosis flag. The charge pump frequency can be modulated with a wobble frequency generator to optimize EMC performance.

## 2.4 Standby mode (EN)

The EN input has an internal pull-down resistor. The device is in standby mode if EN input is set to logic low level. In this case the voltage regulator, the charge pump and all of the outputs are turned off, registers content is also set to default value.

If EN is set to logic high level then the device enters the active mode after a start-up time equal to tstart. In active mode all functions are available and the device is controlled by the ST SPI interface and the digital control pins.

# 2.5 Application block diagram

100n CP-External supply V5V 220n Voltage V3V regulator VDD 100n OUTA1 M CSN OUTA2 SCK L99SM81V SDI SDO OUTB1 ΕN μC OUTB2 CTRL1 CTRL2 CTRL3 AOUT DOUT1 PGND DOUT2 Optional connection

Figure 5: Stepper motor driver application block diagram

As it can be seen from the application block diagram, the device may be driven either by Serial Peripheral Intreface (SPI) or by digital inputs/outputs.

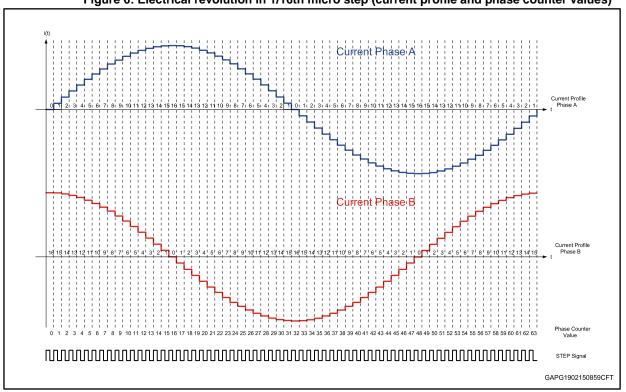

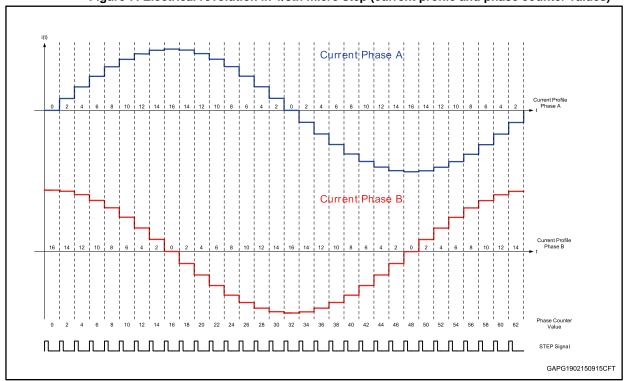

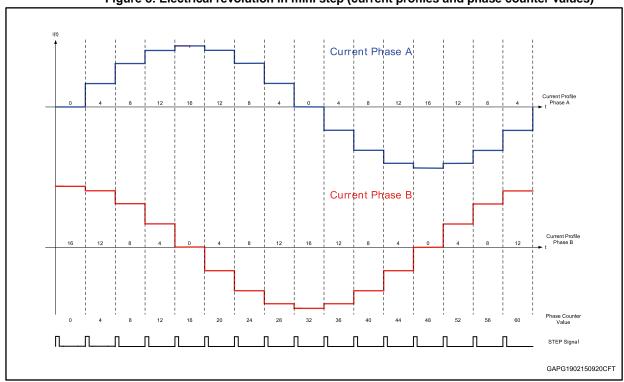

## 2.6 Stepping modes and step update

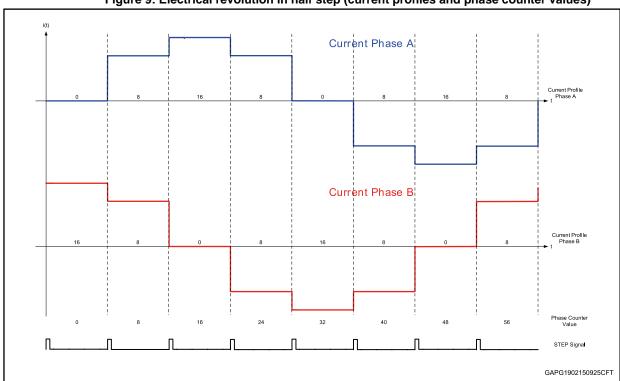

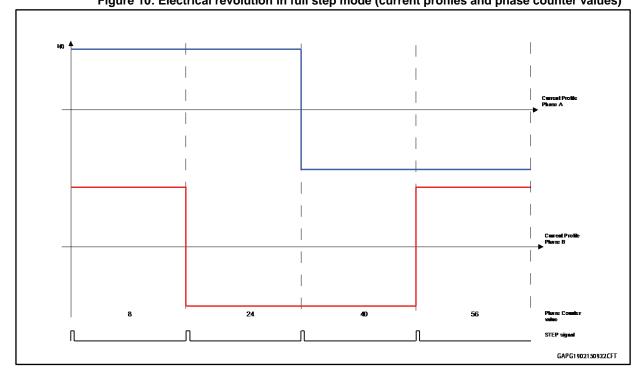

Depending on desired step resolution - as shown in Figure 6: "Electrical revolution in 1/16th micro step (current profile and phase counter values)" to Figure 10: "Electrical revolution in full step mode (current profiles and phase counter values)" - one stepper motor electrical cycle can consist of 64 micro steps (1/16th micro step mode), 32 micro steps (1/8th micro step mode), 16 mini steps (mini step mode), 8 half steps (half step mode) or 4 full steps (full step mode).

Figure 6: Electrical revolution in 1/16th micro step (current profile and phase counter values)

Figure 7: Electrical revolution in 1/8th micro step (current profile and phase counter values)

Figure 8: Electrical revolution in mini step (current profiles and phase counter values)

Figure 9: Electrical revolution in half step (current profiles and phase counter values)

Figure 10: Electrical revolution in full step mode (current profiles and phase counter values)

The current profile generated by the device depends on the phase counter value (stored in PH[5:0] bits in MCR1 register) and it can be altered in an exclusive way either via the SPI interface (MX1 bit = 0) by directly writing PH[5:0] bits or through the CTRL1 pin (MX1 bit = 1) on each rising edge.

Phase counter update becomes effective on next PWM period.

In case MX1 bit is set, user has read-only rights to PH[5:0] bits and the phase counter can only be updated through rising edges on CTRL1 pin. In particular, PH[5:0] is incremented or decremented (depending on running motor direction) by a quantity automatically computed and dependent on the applied Step mode (normally SM[2:0]). Additionally, in case MX3[1:0] (in GCR1 register) is equal to 0x01, the CTRL3 pin can also be used to simultaneously select whether the current Step mode is the one specified by SM[2:0] bits or ASM[2:0] bits (MCR1 register). The automatic increment/decrement of the phase counter amounts to 1 LSB in case of 1/16th microstep mode (SM[2:0] or ASM[2:0] equal to 0x00), 2LSBs in case of 1/8 th microstep mode (SM[2:0] or ASM[2:0] equal to 0x01), 4 LSBs in case of mini-step mode (SM[2:0] or ASM[2:0] equal to 0x02), 8 LSBs in case of half-step mode (SM[2:0] or ASM[2:0] equal to 0x04).

Whenever changing the step mode from a higher resolution to a lower one, the phase counter is adjusted to the next closer phase counter value coherently with the new Step mode. This adjustment is actually applied on the first PWM period after a phase counter change command.

On the contrary, in case MX1 bit is reset, phase counter can only be accessed via SPI and logic level on CTRL1 input is discarded. In order to ensure the maximum flexibility for the application, the computation of the next phase counter value to be written in PH[5:0] is totally left to the application microcontroller. The step mode control bits, which will usually have no impact on the current profile generation when the PHase counter is updated via SPI, will impact the current profile generation only in full step mode.

Any modification of the step mode (either through CTRL3 pin in case MX3[1:0]=0x01 or through SPI writing of bit SM[2:0] and ASM[2:0] in MCR1 register) becomes effective at the beginning of the first PWM cycle following a phase counter update command (either received via CTRL1 pin with MX1=1 or through a SPI writing of PH[5:0] bits with MX1=0).

## 2.7 Current references generation and PWM regulation

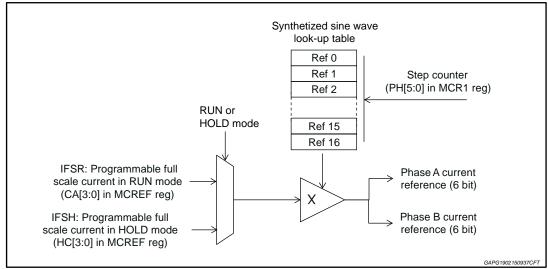

L99SM81V embeds a look-up table composed by 17 entries synthetizing a quarter of a sinusoidal cycle; table elements have 6 bit accuracy. In 1/16th microstep mode each of these table entries represent the value that, once multiplied by the full scale factor stored into CA[3:0] bit of MCREF register, constitute in RUN mode the digital current references for a whole micro step. In HOLD mode, bits HC[3:0] are automatically used instead as full scale factor (see *Figure 11: "Current reference generation block diagram"*).

Figure 11: Current reference generation block diagram

Due to the symmetry of the sinusoidal waveform, all the 64 target motor current pairs of an electrical revolution (in 1/16th micro step) can be referenced by both the 17 table entries and the phase counter register. The 6 bit step (phase) counter - in fact - defines both the sign of the current flowing through phases A and B and which of the 17 current entries is to be used for current reference computation

In full step mode - the full scale current defined by either CA[3:0] or HC[3:0] bits in MCREF is entirely applied to the two motor phases (sine-wave look-up table not used), being current direction dependent on step counter value (see *Figure 10: "Electrical revolution in full step mode (current profiles and phase counter values)"*).

In order to achieve the motor current regulation, the current references generated in this way are then compared with the internal motor current mirror (no external shunt resistor).

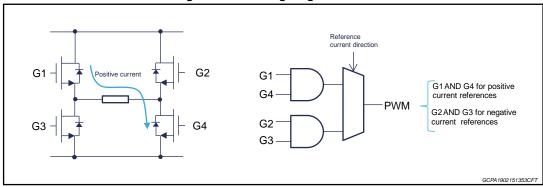

At the beginning of each PWM period, H-bridges A and B are actively driven (PWM ON phase) until the related current reference is reached.

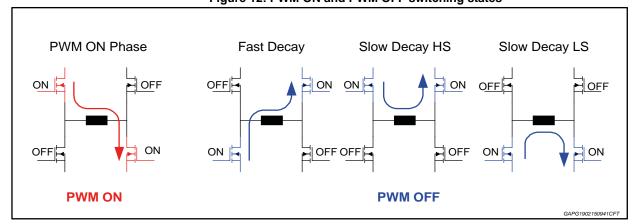

Once a H-bridge reaches its current reference, it is switched to one of the two possible PWM OFF configurations depending on the selected decay mode (see *Figure 12: "PWM ON and PWM OFF switching states"* for an overview of the switching states).

The PWM frequency for the current regulation is configurable (MCR2 FREQ[1:0]) and can be modulated with a wobble frequency generator by activating this option via SPI (GCR1 MWBE).

In order to avoid spurious misleading triggering of the comparator used for the current regulation loop, a minimum PWM on-time, equal to the sum of the programmable comparator blanking time ( $t_B$ ) plus the glitch filter delay time ( $t_{TF}$ ), is always applied.

#### 2.8 HOLD mode

The L99SM81V features a HOLD mode intended to be used when it's required to hold the motor in a given position; HOLD mode is entered either by setting via SPI the HOLDM bit in register MCR1 (if MX3[1:0]  $\neq$  10b) or by setting a logic high value on pin CTRL3 (if MX3[1:0] = 10b).

In case bit AHMSD in MCR3 register is set, then HOLDM bit is set automatically (regardless of MX3 bits value and CTRL3 input level) after a stall condition is detected for a number of consecutive times equal to SD[2:0] (in this case it's necessary either to clear the SDF bit in the Status Register or to reset the AHMSD in the MCR3 Register before HOLDM bit can be cleared).

#### When In HOLD mode:

- The motor current reference is computed automatically for both motor phases starting from the full scale factor stored in bits HC[3:0] of MCREF register.

- The applied decay mode is set accordingly to DMH bit in MCR2

- The PH[5:0] bits can be still updated unless the HOLDM bit is set because of the AHMSD control bit set to one on a stall event detection pointed out by the SDF flag; only in this latter case the phase counter will be frozen as long as both bits (SDF and AHMSD) are set.

#### 2.9 Decay modes

This device features different types of current decay modes. They are implemented to allow a flexible adaptation of the current regulation loop properties to the application requirements. The decay mode can be selected via SPI register MCR2 (DMR[1:0] bits for RUN mode, DMH bit for HOLD mode).

Figure 12: "PWM ON and PWM OFF switching states" shows an overview of the basic switching states during the PWM ON phase and the PWM OFF phase. Each decay mode is a combination of these basic switching states with different trigger events.

Figure 12: PWM ON and PWM OFF switching states

For the slow decay state it is configurable which freewheeling current path will be used (either high-side or low-side) see SPI Register MCR2 SDAFW&SDBFW.

In Fast Decay state the opposite switches in each half - bridge are active – like when driving the current in the opposite direction in PWM ON phase. This allows decreasing the motor phase current faster if compared to Slow Decay but results in a higher current ripple.

In order to combine the advantages of a low current ripple with those of a fast and responsive current regulation, L99SM81V features a dedicated configuration (auto decay mode 2) in which the decay mode is dynamically and automatically adjusted by the device as described in Section 2.9.4: "DMR[1:0] bits = 11b - Auto decay mode 2".

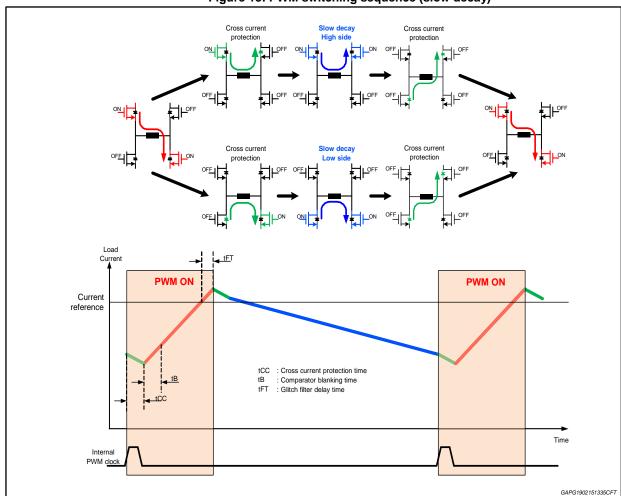

#### 2.9.1 DMR[1:0] bits = 01b, DMH = 0 - Slow decay mode always applied

If DMR[1:0] bits are equal to 01b, Slow Decay Mode is always applied in RUN mode after the PWM ON phase. Likewise, slow decay mode is also always applied in HOLD mode if DMH = 0.

Figure 13: PWM switching sequence (slow decay)

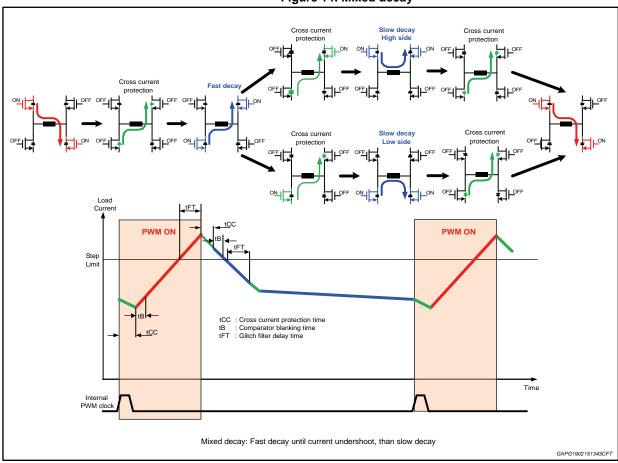

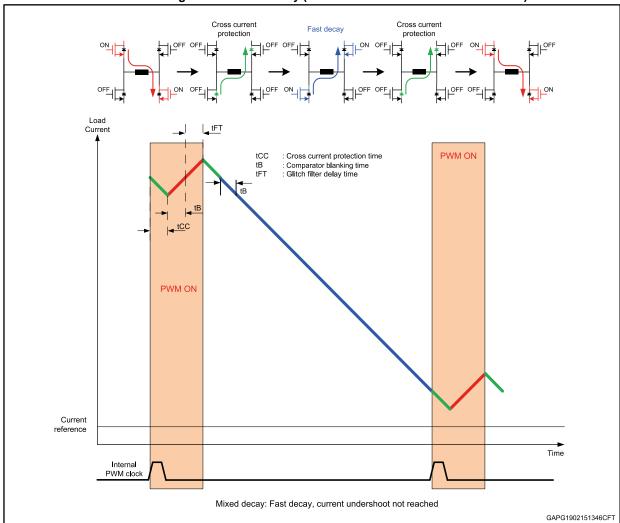

#### 2.9.2 DMR[1:0] bits = 10b, DMH = 1 - Mixed decay mode always applied

If DMR[1:0] bits are equal to 10b, Mixed Decay Mode is always applied in RUN mode. Likewise, mixed decay mode is also always applied in HOLD mode if DMH = 1. In Mixed Decay Mode the PWM ON phase is followed by a fast decay state, which is followed in turn by a slow decay. The start of the slow decay is triggered as soon as the actual current crosses the reference current and the filter time  $t_{\text{FT}}$  has elapsed.

Figure 14: Mixed decay

Figure 15: Mixed decay (current undershoot / limit not reached)

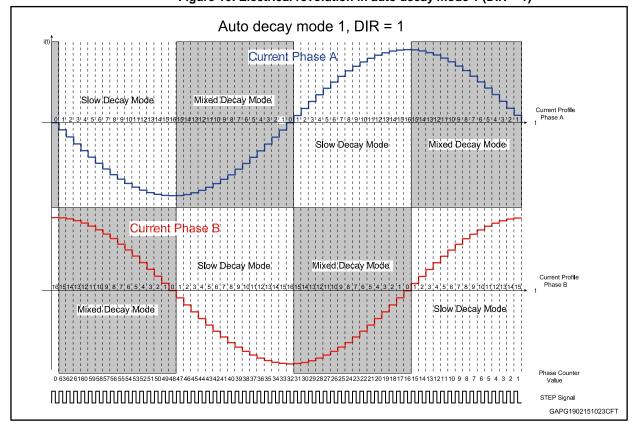

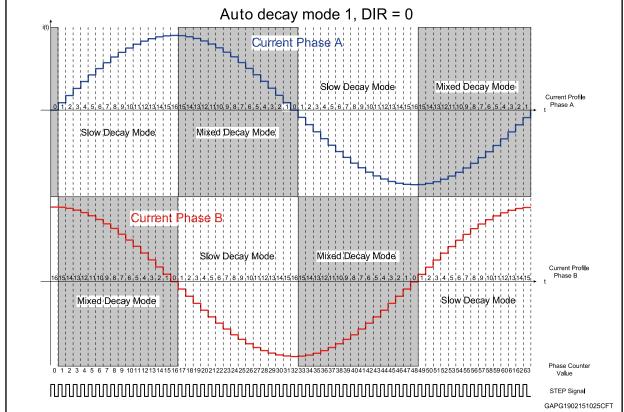

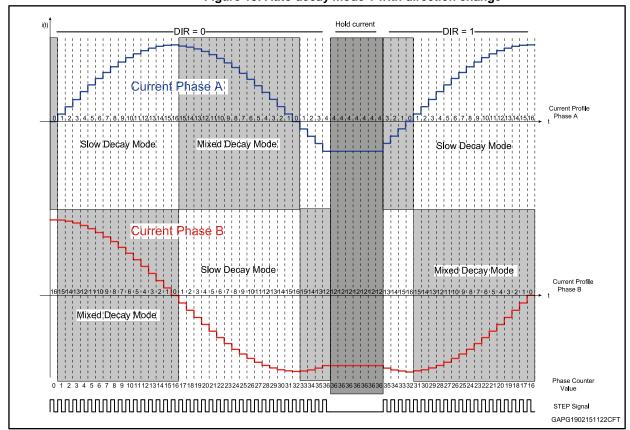

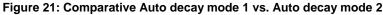

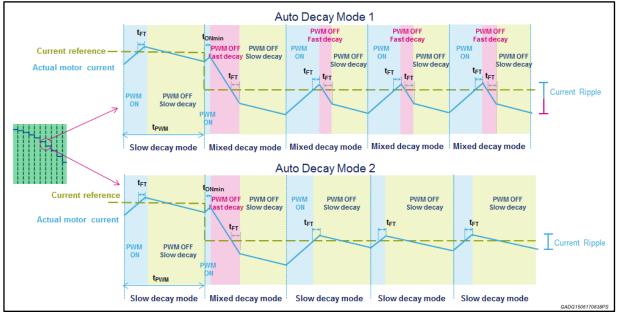

#### 2.9.3 DMR[1:0] bits = 00b - Auto decay mode 1

In Auto Decay Mode1 the phase counter value and the motor spinning direction (DIR bit) are taken into account to select the appropriate switching state specifically, either a slow decay or a mixed decay are applied.

The next two figures show the dependency of the applied decay mode from the phase counter and the direction bit. See also paragraph Section 2.9.2: "DMR[1:0] bits = 10b, DMH = 1 - Mixed decay mode always applied" for mixed decay mode description.

Figure 16: Electrical revolution in auto decay mode 1 (DIR = 1)

Figure 17: Electrical revolution in auto decay mode 1 (DIR = 0)

Figure 18: Auto decay mode 1 with direction change

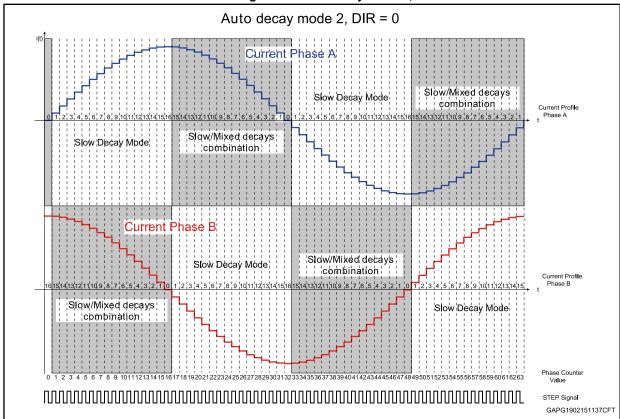

#### 2.9.4 DMR[1:0] bits = 11b - Auto decay mode 2

Auto decay mode 2 allows combining at the best the advantages of a low current ripple together with those of a fast and responsive current regulation. In Auto Decay Mode2, the phase counter value, the motor spinning direction (DIR bit) and the status of the real current vs. the current reference are taken into account to select the appropriate switching state. Figure 19: "Auto decay mode 2, DIR = 0" shows the dependence of the decay mode from the phase counter in case DIR=0 (applied decay mode are opposite in case of DIR =1)

In particular, with reference to the areas where a combination of slow and mixed decay modes is applied, mixed decay is used - in order to achieve the fastest current responsiveness - as soon as a new step begins and till the moment the motor phase current crosses the new (lower in absolute value) current reference, slow decay is then applied in order to reduce the switching losses and the current ripple vs. the mixed decay mode. See also paragraph Section 2.9.2: "DMR[1:0] bits = 10b, DMH = 1 - Mixed decay mode always applied" for mixed decay mode description.

Figure 19: Auto decay mode 2, DIR = 0

New current reference crossed within t  $t_{FT}$ t<sub>ON min</sub> **Current reference** PWM OFF **PWM OFF** PWM ON PWM OFF Fast decay Slow decay Slow decay **Actual motor current** PWM OFF ON Slow decay Slow decay mode | Mixed decay mode | Slow decay mode New current reference crossed within 2 x t  $t_{FT}$ t<sub>ON min</sub> **Current reference PWM OFF** PWM OFF PWM **PWM OFF** Slow decay Fast decay Slow decay **Actual motor current** PWM OFF Fast decay **PWM OFF PWM**  $\mathbf{t}_{\text{FT}}$  $t_{FT}$ Slow decay ON Slow decay mode | Mixed decay mode | Mixed decay mode | Slow decay mode

Figure 20: Auto decay mode 2, behavior at micro-step change (dead-time omitted)

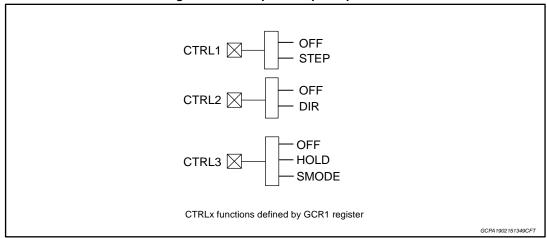

## 2.10 Control pins (CTRLx)

Some of the functions in the L99SM81V can be controlled directly by application microcontroller I/Os (without using SPI communications) through the CTRLx digital input pins. The action to be executed by these pins is defined by MX bits in GCR1 registers.

Figure 22: CTRL pin multiplex options

#### 2.10.1 Step Control (STEP)

If MX1 bit in GCR1 register is reset, no function is associated to the CTRL1 pin. Any step change can only be achieved by writing to the SPI PH[5:0] bits via SPI. If MX1 bit is set, a rising edge on this digital input causes the phase counter to be immediately updated (according to DIR bit) whereas the reference current is updated with the new value at the beginning of next PWM cycle (PH[5:0] can only be read through SPI in this case). If the DIR bit in the motor control register is reset then the phase counter will be incremented; if the DIR bit is set, then the phase counter will be decremented.

The decrement or increment value depends on the currently applied Step mode.

#### 2.10.2 Direction Control (DIR)

If MX1 bit is reset in GCR1 register, the update of the phase counter (via SPI) is totally left to the application microcontroller. As a consequence, whatever is the value of MX2 bit, the direction is thus as well managed by the external microcontroller.

If MX1 is set, CTRL1 input holds the STEP functionality; the motor spinning direction is set in this case either via SPI or through direct input (CTRL2) depending on the value of MX2 bit

If MX2 bit in GCR1 register is reset, no function is associated to the CTRL2 pin; DIR bit in MCR1 can only be written through SPI in this case.

If MX2 bit is set, the DIR bit can only be altered by CTRL2 pin: a high (low) logic level on this digital input will cause the direction bit DIR to be synchronously set (reset).

#### 2.10.3 Step mode Control (SMODE) and HOLD mode

If MX3[1:0] bits in GCR1 register are equal to 0x00 or 0x03, no function is associated to the CTRL3 pin. The Step mode utilized in this case is either defined by SM[2:0] bits (MX1 bit = 1) or left to application microcontroller (MX1 bit = 0, full step mode apart). HOLD mode is entered by setting HOLDM bit in MCR1 through SPI.

If MX3[1:0] bits in GCR1 register are equal to 0x01, CTRL3 input selects the Step mode to be used: if CTRL3 = 0, the active step mode is the one defined by SM[2:0], otherwise the

active step mode is the one defined by ASM[2:0]. To be noticed that if MX1 is reset, Step mode is intrinsically managed by the application microcontroller as it defines by itself the amount of increment or decrement to be applied on the phase counter. HOLD mode is entered by setting HOLDM bit in MCR1 through SPI.

If MX3[1:0] bits in GCR1 register are equal to 0x02, CTRL3 pin is used as HOLD input, HOLDM bit reflects the logic state on CTRL3 and can't be altered through SPI. In case AHMSD is set, HOLDM bit is set in case of stall detection (SDF flag set) independently from CTRL3 pin logic level.

## 2.11 Digital outputs

The device features several diagnostic functions that can be reported to the microcontroller without starting an SPI communication. These signals can be assigned to device outputs by programming SPI configuration bits [11:7] in register GCR2.

If bits DOUT1[1:0] or DOUT2[1:0] in GCR2 register are set to 00b, the device will not drive the corresponding DOUTn pin.

DOUT1 OFF

CVRDY

CVLL

CVRUN

OFF

PWM

ERR

EC

Figure 23: Configurable I/O multiplex options

#### 2.11.1 Error/ warning indicator (ERR)

This signal is a logical OR combination of all diagnostic and warning flags contained in Global Status Register (GSR).

#### 2.11.2 Error/ warning change indicator (EC)

This signal is set every time any of the diagnostic and warning flags contained in GSR is set. Any read access to the GSR register will reset this signal to low level.

#### 2.11.3 PWM

As shown in *Figure 24: "PWM signal generation"* this signal reflects the PWM control signal applied to the H-bridge A outputs.

Figure 24: PWM signal generation

#### 2.11.4 Coil Voltage Conversion Ready (CVRDY)

A rising edge on this signal indicates that averaged coil voltage measurement is available in the respective MCV register.

A falling edge on this signal occurs when a new zero-current micro-step begins.

#### 2.11.5 Coil Voltage Runaway (CVRUN)

CVRUN signal is updated every time a new coil voltage measurement is available. If the latest stored coil voltage value is higher than CVUL threshold or lower than CVLLA threshold, the signal is set, otherwise is reset.

#### 2.11.6 Coil Voltage Lower Limit Underrun (CVLL)

CVLL signal is updated every time a new coil voltage measurement is available (rising edge of signal CVRDY). If the latest stored coil voltage value is lower than CVLLB, the signal is set, otherwise it is reset.

## 2.12 Analog output

The device features an analog output which - depending on AOUT[1:0] bits in GCR1 register - can be used either to feed back the device embedded thermal sensor output (AOUT[1:0]=01b) or a precise band-gap voltage reference (AOUT[1:0]=10b).

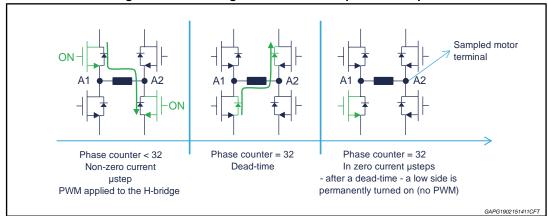

#### 2.13 Motor coil voltage measurement for stall detection

Setting CVE bit in MCR3 enables the automatic measurement of the voltage across the motor terminals during each zero-current step; this makes it possible to measure the voltage induced by the rotor movement (BEMF) and thus have information about motor speed.

In order for the motor coil voltage measurement to be correctly performed, it's required that bit MWBE in GCR1 is reset.

Four BEMF values are converted within a complete electrical cycle (*Figure 25: "Coil voltage registers content (DIR = 0, positive current flowing from OUTx1 to OUTx2; x = A, B)"*), related digital values are stored into registers MCVA, MCVB, MCVC, MCVD and bits CVLUR[1:0] in MCR3 indicate which of MCVx registers was lastly updated.

The motor terminal to be sampled is automatically selected depending on the rotation direction and on phase counter value so that only positive BEMF is always measured (see also *Table 2: "Coil voltage synopsis table"*).

Figure 25: Coil voltage registers content (DIR = 0, positive current flowing from OUTx1 to OUTx2; x = A, B)

In order for the sampled coil voltage to be really equal to the BEMF induced by the rotor, the PWM signals applied to the H-bridge driving the coil under examination are switched off as soon as the zero-current step begins. In addition - after a dead-time and according to Table 2: "Coil voltage synopsis table" - the low side power switch opposite to the output to be converted is switched on (see Figure 26: "Coil voltage measurement sequence example") in order to have coil voltage measurement referred to GND.

Figure 26: Coil voltage measurement sequence example

Table 2: Coil voltage synopsis table

|               | DIR bit = 0<br>(phase counter increasing) |                        |                  |                        |                  |

|---------------|-------------------------------------------|------------------------|------------------|------------------------|------------------|

| Phase counter | Output to<br>GND                          | Motor terminal sampled | Output to<br>GND | Motor terminal sampled | Updated register |

| 0             | A2                                        | A1                     | A1               | A2                     | MCVA             |

| 16            | B1                                        | B2                     | B2               | B1                     | MCVB             |

| 32            | A1                                        | A2                     | A2               | A1                     | MCVC             |

| 48            | B2                                        | B1                     | B1               | B2                     | MCVD             |

#### 2.13.1 Coil voltage measurement triggering

In order to filter out any PWM commutation noise, several A/D conversions are carried out and averaged over each PWM period (the number of averaged samples ranges from 8 to 16, depending on programmed PWM frequency). The digital averaged value is then transferred into proper MCVx register on a triggering event which depends on bits D[4:0] in register MCR3:

- D[4:0] = 00000b; trigger at the end of the zero-current step.

Digital averaged coil voltage is transferred into MCVx register at the end of a zero current step (that is as soon as a step counter change becomes effective, default option).

- 2. D[4:0] > 00001b; trigger delayed from the start of the zero-current step. During a zero-current step, the digital averaged coil voltage is transferred into MCVx register after a given number of PWM cycles defined by bits D[4:0] in register MCR3 have elapsed. In case the step counter update command is given before the programmed PWM cycles have elapsed, the zero-current step duration is extended till that time, thus delaying the actual phase counter update.

#### 2.13.2 Coil voltage measurement processing

As soon as the triggering event occurs, both proper MCVx register and bits CVLUR[1:0] in MCR3 (indicating which of MCVx registers lastly changed) are updated. Also, CVRDY signal goes from low to high (falling edge of CVRDY signal indicates that zero-current step has started).

As soon as a new value is stored into MCVx register, the same value is automatically compared with user-configurable thresholds:

47/

- CVUL, stored in MCVUL register

- CVLLA, stored in MCVLLA register

- CVLLB, stored in MCVLLB register

Depending on the comparison result, flags CVULF, CVLLAF and CVLLBF are also updated in MSR:

- CVULF is set if sampled coil voltage exceeds CVUL threshold, it is reset otherwise

- CVLLAF is set if sampled coil voltage falls below CVLLA threshold, it is reset otherwise

- CVLLBF is set if sampled coil voltage falls below CVLLB threshold, it is reset otherwise

#### Additionally

- CVRUN signal is set if latest stored coil voltage value is higher than CVUL or lower than CVLLA, it is reset otherwise

- CVLL signal is set if the latest sampled coil voltage value is lower than CVLLB, it is reset otherwise

If the sampled coil voltage value is out of the range [CVLLA; CVUL] for a number of consecutive acquisitions (zero-current steps) equal to SD[2:0], then the bit SDF of the GSR is set. If the bit AHMSD in MCR3 register is set, then the HOLDM bit (in MCR1) is also automatically set and the driver enters HOLD mode. See also Section 2.8: "HOLD mode" for more information about HOLD mode.

The SDF status flag is also reported in the Global Status Byte as FE.

## 2.14 Serial peripheral interface (ST SPI standard)

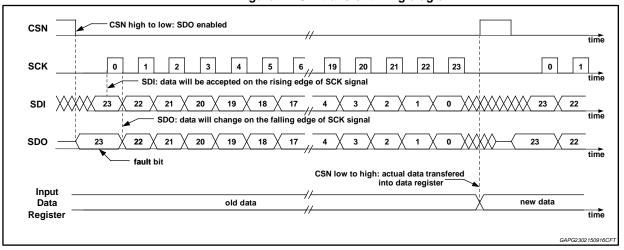

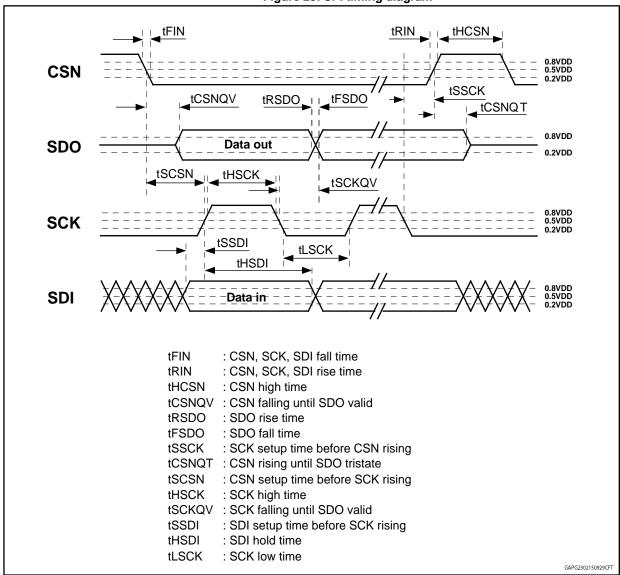

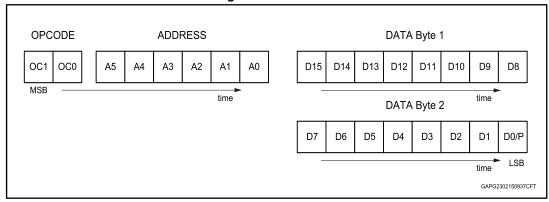

This device features a 24-bit ST SPI in slave configuration for bi-directional communication with an external microcontroller. This device supports burst read access and shall be operated in the following mode: CPOL = 0 and CPHA = 0.

For this mode, input data is sampled on the rising edge of the clock signal SCK and output data is changed on the falling edge of SCK.

During standby mode, the SPI interface is deactivated.

#### Signal Description:

- Chip Select Not (CSN)

- The input pin is used to select the serial interface of this device. When CSN is high, the output pin (SDO) will be in high-impedance state. In case CSN is stuck at GND, a timeout is implemented which sets the SDO line back to high-impedance to release the SPI network. A low signal activates the output driver and a serial communication can be started. The state during CSN = 0 is called a communication frame.

- Serial Data In (SDI)

- The input pin is used to transfer data serially into the device. The data applied to SDI will be sampled on the rising edge of the SCK signal and shifted into an internal 24-bit shift register. On the rising edge of the CSN signal, the contents of the shift register will be transferred to the Data Input Register. Only communication frames with 0 (read GSBN bit), 24 (standard communication frame), or 24 + (n \* 16) (burst read/write) clock pulses are accepted. All others will be ignored and a communication error will be reported with the next SPI command.

- Serial Data Out (SDO)

- The data output driver is activated by a logic low level at the CSN input. After a falling edge of the CSN pin, the SDO pin will leave the tri-state condition and present the GSBN bit. At all following falling edges of the SCK signal, the following bits of the SPI frame are shifted out to the SDO pin.

Serial Clock (SCK)

The SCK input is used to synchronize the input and output serial bit streams. The data input (SDI) is sampled on the rising edge of the SCK and the data output (SDO) will change with the falling edge of the SCK signal. The SPI can be driven with a SCK frequency up to 4 MHz.

## 3 Protections and diagnostics

#### 3.1 Supply diagnostics

#### 3.1.1 VS overvoltage and undervoltage

If the voltage on the supply pins VS rises above the overvoltage threshold, VSOV flag in GSR register is set and latched, the charge pump is switched off and ME bit (MCR1 register) is cleared, thus putting the device outputs in high impedance. VS has to drop below the overvoltage threshold minus the over-voltage hysteresis to allow the clearing of VSOV bit.

Likewise, if the voltage on the supply pins VS falls below its undervoltage threshold, the corresponding undervoltage diagnosis flag (VSUV bit in GSR register) is set, ME bit is cleared and charge pump is switched off. VSUV bit can be cleared (and consequently, ME bit can be set) by the microcontroller when VS voltage has risen above the undervoltage threshold plus the undervoltage hysteresis.

#### 3.1.2 VREG overvoltage and undervoltage

If the voltage on the supply pin VREG rises above its overvoltage threshold, the corresponding overvoltage diagnosis flag (VREGOV bit in GSR register) is set and the V5V regulator is switched off. VREGOV bit can be cleared by the microcontroller when VREG voltage has dropped below the overvoltage threshold minus the overvoltage hysteresis.

If the voltage on the supply pin VREG falls below its undervoltage threshold warning, the corresponding undervoltage diagnosis flag (VREGUV bit in GSR register) is set. VREGUV flag can be cleared by the microcontroller when VREG voltage has risen above the undervoltage threshold plus the undervoltage hysteresis. If VREG voltage decreases further below the VREG POR threshold, the device is reset and the registers are reset to their default value.

#### 3.1.3 CP failure

The charge pump operation is internally monitored. If the charge pump voltage falls below the VCPLOW threshold, the CP failure flag CPFAIL in GSR is set and the charge pump is switched off. This clear also the ME bit, thus disabling the output drivers. The CP failure flag can be cleared through a dedicated Read & Clear SPI command. Once the flag is cleared, the ME bit can be set.

#### 3.1.4 V5V undervoltage warning

If the output voltage on pin V5V drops below the undervoltage warning threshold V5UVW, the V5V undervoltage warning flag V5UVW in GSR is set.

This flag can be cleared by a Read & Clear SPI command.

#### 3.1.5 V5V failure

If the output voltage on pin V5V rises above the V5V overvoltage threshold (V5VOV), then the V5V failure flag is set and the voltage regulator is disabled.

In case the 5V regulator output drops below the V5VFAIL threshold, the L99SM81V detects a short circuit to ground, the V5V failure flag (V5VUV) is latched and the voltage regulator is disabled. If the output of the regulator doesn't exceed the V5VFAIL threshold after a time equal to t<sub>FTO</sub>, the device detects a short-circuit condition, the regulator is switched off and

the corresponding failure flag is set. To re-enable the voltage regulator, the failure flag has to be cleared.

#### 3.1.6 VDD failure

In case VDD voltage falls below the threshold VDDPORF, the internal registers are reset to their default values. The power-on reset is released once VDD rises above VDDPORR.

### 3.2 Thermal warning and thermal shutdown

If the junction temperature reaches the TW threshold, the TW flag in GSR is set and latched. In case the junction temperature increases and reaches the TSD threshold, the two full-bridges, the charge pump and the voltage regulator V5V are disabled to protect the device and the TSD flag in GSR is set and latched. In order to re-enable the driver, the junction temperature must decrease below the thermal shutdown threshold, the thermal shutdown error flag must be cleared by the microcontroller and the ME bit must be set again.

## 3.3 Cross current protection (dead-time)

The device features an internal dead-time generator for cross current protection. The duration of the dead-time is automatically adjusted according to the SR[1:0] bits in MCR2 register which set the turn-on and turn-off speed of the integrated power MOSFETs.

## 3.4 Driver diagnostic

#### 3.4.1 Overcurrent detection

If the current through any of the switches in the output driver exceeds the output overcurrent limit IOCxn for longer than tOC, then the corresponding overcurrent error flag in the motor status register MSR is set and the outputs are set in high impedance state (ME bit reset in MCR1).

To re-enable the output drivers, the error flag OC has to be cleared in GSR by the application microcontroller and the ME bit must be set again.

#### 3.4.2 Open load detection

Starting from the beginning of any PWM cycle, if the motor current doesn't reach the current reference for a period of time longer then a programmable delay (OLDLY bit in MCR2), then the corresponding open load flag (OLA or OLB bits, depending on which of the motor phase is failing) is set in MSR register.

These flags don't affect the output drivers and can be cleared by clearing the OL flag in GSR.

## 4 Electrical characteristics

# 4.1 Absolute maximum ratings

Table 3: Absolute maximum ratings

| Symbol                                               | Parameter                                                                 | Value                                                              | Unit |

|------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------|------|

| VS                                                   | Power supply voltage                                                      | -0.3 to 40                                                         | V    |

| VREG                                                 | Voltage regulator power supply                                            | -0.3 to 40                                                         | V    |

| VDD                                                  | Digital I/Os supply                                                       | -0.3 to 6                                                          | V    |

| V5V                                                  | Voltage regulator output                                                  | -0.3 to 40                                                         | V    |

| VCP, CP+                                             | Charge pump output voltage, positive connection for charge pump capacitor | VSA - 0.3 to 45 V (in case VSA >28V) or VSA +17 V (in case VSA<28) | V    |

| CP-                                                  | Charge pump pin for negative capacitor connection                         | -0.3 to VSA+0.3 V                                                  | V    |

| VOUTxn                                               | Output voltage (x = A,B; n = 1,2)                                         | -0.3 to VS + 0.3                                                   | V    |

| VEN, VCTRLn,<br>VDOUTn,<br>VSDO, VSDI,<br>VCLK, VCSN | Logic I/O voltage range (x = 1,2;<br>n = 1,2,3)                           | -0.3 to 6                                                          | ٧    |

| AOUT                                                 | Analog output                                                             | -0.3 to 40                                                         | V    |

All maximum ratings are absolute ratings. Exceeding any of these values may cause an irreversible damage of the integrated circuit!

# 4.2 Operating range

**Table 4: Operating range**

| Symbol                                         | Parameter                                           | Value    | Unit     |

|------------------------------------------------|-----------------------------------------------------|----------|----------|

| VS                                             | Power supply voltage                                | 6 to 28  | V        |

| VREG                                           | Voltage regulator power supply                      | 6 to 28  | <b>V</b> |

| VDD                                            | Digital I/Os supply                                 | 3 to 5.5 | V        |

| VEN, VCTRLn, VDOUTn,<br>VSDO, VSDI, VCLK, VCSN | Logic I/O voltage range ( $x = 1,2$ ; $n = 1,2,3$ ) | 0 to VDD | ٧        |

# 4.3 ESD protection

**Table 5: ESD protection**

| Parameter                                                                                 |      |    |

|-------------------------------------------------------------------------------------------|------|----|

| Electrostatic Discharge Test (AECQ100-002-E) all pins                                     | ±2   | kV |

| Electrostatic Discharge Test (AECQ100-002-E) output pins VOUTKXN (X = A,B; N, $K = 1,2$ ) | ±4   | kV |

| Charge device model (CDM-AEC-Q100-011) all pins                                           | ±500 | V  |

| Charge device model (CDM-AEC-Q100-011) corner pins                                        | ±750 | V  |

Electrical characteristics L99SM81V

#### 4.4 Thermal data

Table 6: Thermal data

| Symbol                 | Parameter                                  | Test condition      | Min. | Тур. | Max. | Unit |

|------------------------|--------------------------------------------|---------------------|------|------|------|------|

| T <sub>stg</sub>       | Storage temperature                        |                     | -55  |      | 150  | °C   |

| Tj                     | Operating junction temperature             |                     | -40  |      | 150  | °C   |

| T <sub>j-peak</sub>    | Peak junction temperature (1)              |                     |      | 160  |      | °C   |

| R <sub>th</sub> j-amb  | Junction-to-ambient thermal resistance (2) | PowerSSO-36 package |      | 17   |      | °C/W |

|                        |                                            | QFN40L package      |      | 23   |      |      |

| R <sub>th j-case</sub> | Junction-to-case thermal resistance        | PowerSSO-36 package |      | 5    |      | °C/W |

|                        |                                            | QFN40L package      |      | 6.5  |      | °C/W |

#### Notes:

Table 7: Thermal warning and thermal shutdown

| Symbol           | Parameter                     | Test condition       | Min. | Тур. | Max. | Unit |

|------------------|-------------------------------|----------------------|------|------|------|------|

| TW               | Thermal warning threshold (1) |                      | 140  | 150  | 160  | °C   |

| TSD              | Thermal shutdown threshold    |                      | 160  | 170  | 180  | °C   |

| TSDH             | Thermal shutdown hysteresis   |                      |      | 5    |      | °C   |

| t <sub>TFT</sub> | Thermal filter time           | Tested by scan chain |      | 64   |      | μs   |

#### Notes:

#### 4.5 Main electrical characteristics

Voltages are referred to ground and currents are assumed positive when the current flows into the pin.

The device is operated in the specified operating range, unless otherwise specified.

Table 8: Supply and supply monitoring

| Symbol | Parameter                                 | Test condition | Min. | Тур. | Max. | Unit |

|--------|-------------------------------------------|----------------|------|------|------|------|

| VSOV   | Overvoltage<br>threshold on VS<br>supply  |                | 28.1 | 30   | 32   | V    |

| VSOVH  | Overvoltage<br>hysteresis on VS<br>supply |                | 0.5  |      |      | V    |

| VSUV   | Undervoltage<br>threshold on VS<br>supply |                | 5.2  | 5.5  | 5.9  | V    |

$<sup>^{(1)}</sup>$ No more than 100 cumulative hours over lifetime.

<sup>(2)</sup> Device soldered on 2s2p PCB thermally enhanced (slug included).

<sup>&</sup>lt;sup>(1)</sup>Thermal warning and shutdown thresholds not overlapping.

| Symbol           | Parameter                                            | Test condition                                                                                        | Min. | Тур. | Max. | Unit |

|------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------|------|------|------|

| VSUVH            | Undervoltage<br>hysteresis on VS<br>supply           |                                                                                                       | 0.3  |      |      | V    |

| VREGOV           | Overvoltage<br>threshold on<br>VREG supply           |                                                                                                       | 28.1 | 30   | 32   | V    |

| VREGOVH          | Overvoltage<br>hysteresis on<br>VREG supply          |                                                                                                       | 0.5  |      |      | V    |

| VREGUV           | Undervoltage<br>warning threshold<br>on VREG supply  |                                                                                                       | 5.2  | 5.5  | 5.9  | V    |

| VREGUVH          | Undervoltage<br>warning hysteresis<br>on VREG supply |                                                                                                       | 0.3  |      |      | V    |

| t∨FT             | Overvoltage and undervoltage filter time             | Tested by scan chain                                                                                  |      | 64   |      | μs   |

| Is               | VS supply current in active mode                     | VS = 13.5 V; EN = VDD = 5 V;<br>open outputs; SR = 70 V/μs;<br>FREQ[1:0] = 01b<br>(30 kHz PWM)        |      | 4    | 6    | mA   |

| lob              | VDD supply<br>current in active<br>mode              | VS = 13.5 V;<br>EN = CSN = VDD = 5 V;<br>SCK = SDI = STEP = 0 V; open<br>outputs                      |      | 1.2  | 1.8  | mA   |

| IREG             | VREG supply current in active mode                   | VS = VREG = 13.5 V;<br>EN = VDD = 5 V; open outputs;<br>SR = 70 V/µs; FREQ[1:0] = 01b<br>(30 kHz PWM) |      | 7.5  | 12.3 | mA   |

| Isa              | VS quiescent supply current in                       | VS = 13.5 V; VDD = 5 V; EN = 0V; open outputs; T <sub>TEST</sub> = -40 °C to 25 °C;                   |      | 3    | 10   | μΑ   |

|                  | standby mode                                         | VS = 13.5 V; VDD = 5 V EN = 0V; open outputs; T <sub>TEST</sub> = 125 °C;                             |      | 6    | 20   | μΑ   |

| I <sub>DDQ</sub> | VDD quiescent supply current in                      | VS = 13.5 V; VDD = 5 V EN = 0V;<br>open outputs; T <sub>TEST</sub> = -40 °C to<br>25 °C;              |      | 3    | 10   | μΑ   |

|                  | standby mode                                         | $VS = 13.5 \text{ V}$ ; $VDD = 5 \text{ V}$ $EN = 0V$ ; open outputs; $T_{TEST} = 125 \text{ °C}$ ;   |      | 6    | 20   | μΑ   |

| IREGQ            | VREG quiescent supply current in standby mode        | VS = VREG = 13.5 V; VDD = 5 V;<br>EN = 0 V; open outputs                                              |      |      | 5    | μΑ   |

Table 9: Power on reset

| Symbol   | Parameter                 | Test condition      | Min. | Тур. | Max. | Unit |  |

|----------|---------------------------|---------------------|------|------|------|------|--|

| VDDPORR  | Power-on-reset rising     | VDD rising          | 2.2  |      | 2.8  | V    |  |

| VDDPORF  | Power-on-reset falling    | VDD falling         | 2    | 2.3  | 2.5  | V    |  |

| VDDPORH  | Power-on-reset hysteresis | VDD POR hysteresis  | 0.2  |      |      | V    |  |

| VREGPORR | Power-on-reset rising     | VREG rising         | 3.1  | 3.5  | 3.9  | V    |  |

| VREGPORF | Power-on-reset falling    | VREG falling        | 2.9  | 3.3  | 3.8  | V    |  |

| VREGPORH | Power-on-reset hysteresis | VREG POR hysteresis | 25   |      |      | mV   |  |

Table 10: Voltage regulator V5V

| Symbol               | Parameter                                                               | Test condition                                                          | Min. | Тур. | Max. | Unit     |

|----------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------|------|------|------|----------|

| V5V                  | Output voltage                                                          |                                                                         |      | 5.0  |      | V        |

|                      | Output voltage tolerance including line and load regulation             | Active mode;<br>0 mA < I <sub>V5V</sub> <= 40 mA;<br>8 V <= VREG < 28 V | -5   |      | 5    | %        |

| V5V                  |                                                                         | Active mode;<br>0 mA < I <sub>V5V</sub> <= 25 mA;<br>6 V <= VREG < 8 V  | -5   |      | 5    | %        |

| loau regulation      | Active mode;<br>25 mA < I <sub>V5V</sub> <= 40 mA;<br>6 V <= VREG < 8 V | -5                                                                      |      | 5    | %    |          |

| I <sub>V5VP</sub>    | Output peak current                                                     | Max. continuous load current                                            |      |      | 50   | mA       |

| I <sub>V5</sub> VLIM | Short-circuit output current                                            | Current limitation                                                      | 50   |      | 150  | mA       |

| CV5V                 | Load capacitor                                                          | Ceramic (+/- 20%)                                                       |      | 0.22 |      | μF       |

| V5UVW                | Undervoltage warning threshold                                          |                                                                         | 4    | 4.2  | 4.4  | ٧        |

| V5VOV                | Overvoltage threshold                                                   |                                                                         | 5.42 | 5.9  | 6.38 | >        |

| V5VFAIL              | Fail threshold                                                          |                                                                         | 1.8  | 2    | 2.2  | <b>V</b> |

| tuvft                | Undervoltage warning filter time                                        | Tested by scan chain                                                    |      | 16   |      | μs       |

| tovft                | Overvoltage filter time                                                 | Tested by scan chain                                                    |      | 16   |      | μs       |

| t <sub>FFT</sub>     | Fail filter time                                                        | Tested by scan chain                                                    |      | 16   |      | μs       |

| tғто                 | Fail time-out filter (start-up condition)                               | Tested by scan chain                                                    |      | 4    |      | ms       |

L99SM81V Electrical characteristics

Table 11: AOUT electrical characteristics

| Symbol             | Parameter              | Test condition                                         | Min. | Тур.  | Max. | Unit |

|--------------------|------------------------|--------------------------------------------------------|------|-------|------|------|

| VBG                | Output voltage bandgap | T <sub>j</sub> = 25 °C                                 |      | 1.206 |      | V    |

|                    | Whole range accuracy   | -40 °C < T <sub>i</sub> < 150 °C;<br>6 V < VREG < 28 V | -2.5 |       | 2.5  | %    |

| T <sub>SENSE</sub> | Thermal sensor output  | T <sub>j</sub> = 25 °C                                 |      | 1.32  |      | V    |

| 52.752             | Thermal coefficient    |                                                        |      | -4.24 |      | mV/K |

Table 12: OUTxn outputs (x = A,B; n = 1,2)

| Symbol    | Parameter                               | Test condition                                            | Min. | Тур. | Max. | Unit |

|-----------|-----------------------------------------|-----------------------------------------------------------|------|------|------|------|

| D 110     | ON A CUT A MO                           | VS = 13.5 V;<br>T <sub>J</sub> = 25°C;<br>Ixn = -1.25 A   |      | 0.7  | -    | Ω    |

| Rxn_HS    | ON-resistance OUTxn to VS               | VS = 13.5 V;<br>T <sub>J</sub> = 150 °C;<br>Ixn = -1.25 A |      | 1.14 | 1.3  | Ω    |

| Dvo I C   | ON registence OUTvn to BCND             | VS = 13.5 V;<br>T <sub>J</sub> = 25 °C;<br>Ixn = 1.25 A   |      | 0.7  | -    | Ω    |

| Rxn_LS    | ON-resistance OUTxn to PGND             | VS = 13.5 V;<br>T <sub>J</sub> = 150 °C;<br>Ixn = 1.25 A  |      | 1.14 | 1.3  | Ω    |

| IOCxn     | Output overcurrent protection threshold | Static test                                               | 1.9  | 2.2  | 2.75 | Α    |

|           |                                         | CA[3:0] = 0x0F                                            | 1204 | 1353 | 1502 | mA   |

|           |                                         | CA[3:0] = 0x0E                                            |      | 1160 |      |      |

|           |                                         | CA[3:0] = 0x0D                                            |      | 1051 |      |      |

|           |                                         | CA[3:0] = 0x0C                                            |      | 920  |      |      |

|           |                                         | CA[3:0] = 0x0B                                            |      | 812  |      |      |

|           |                                         | CA[3:0] = 0x0A                                            |      | 679  |      |      |

|           |                                         | CA[3:0] = 0x09                                            |      | 571  |      |      |

| <br> IFSR | Full scale current threshold in         | CA[3:0] = 0x08                                            |      | 465  |      |      |

| JII OK    | RUN mode                                | CA[3:0] = 0x07                                            |      | 396  |      |      |

|           |                                         | CA[3:0] = 0x06                                            |      | 375  |      |      |

|           |                                         | CA[3:0] = 0x05                                            |      | 329  |      |      |

|           |                                         | CA[3:0] = 0x04                                            |      | 323  |      |      |

|           |                                         | CA[3:0] = 0x03                                            |      | 302  |      |      |

|           |                                         | CA[3:0] = 0x02                                            |      | 220  |      |      |

|           |                                         | CA[3:0] = 0x01                                            |      | 198  |      |      |

|           |                                         | CA[3:0] = 0x00                                            | 141  | 176  | 211  | mA   |

| IFSH      | Full scale output current in            | HC[3:0] = 0x0F                                            | 290  | 326  | 362  | mA   |

|           | HOLD mode                               | HC[3:0] = 0x0E                                            |      | 292  |      |      |

| Symbol  | Parameter                                                               | Test condition              | Min. | Тур. | Max. | Unit |

|---------|-------------------------------------------------------------------------|-----------------------------|------|------|------|------|

|         |                                                                         | HC[3:0] = 0x0D              |      | 264  |      |      |

|         |                                                                         | HC[3:0] = 0x0C              |      | 230  |      |      |

|         |                                                                         | HC[3:0] = 0x0B              |      | 202  |      |      |

|         |                                                                         | HC[3:0] = 0x0A              |      | 168  |      |      |

|         |                                                                         | HC[3:0] = 0x09              |      | 140  |      |      |

|         |                                                                         | HC[3:0] = 0x08              |      | 118  |      |      |

|         |                                                                         | HC[3:0] = 0x07              |      | 101  |      |      |

|         |                                                                         | HC[3:0] = 0x06              |      | 95   |      |      |

|         |                                                                         | HC[3:0] = 0x05              |      | 84   |      |      |

|         |                                                                         | HC[3:0] = 0x04              |      | 79   |      |      |